#### **General Description**

The MAX9176/MAX9177 are 670MHz, low-jitter, lowskew 2:1 multiplexers ideal for protection switching, loopback, and clock distribution. The devices feature ultra-low 68ps peak-to-peak deterministic jitter that ensures reliable operation in high-speed links that are highly sensitive to timing errors.

The MAX9176 has fail-safe LVDS inputs and an LVDS output. The MAX9177 has "anything" differential inputs (CML/LVDS/LVPECL) and an LVDS output. The output can be put into high impedance using the power-down input. The MAX9176 features fail-safe circuits that drive the output high when a selected input is open, undriven and shorted, or undriven and terminated. The MAX9177 has bias circuits that force the output high when a selected input is open. The mux select and powerdown inputs are compatible with standard LVTTL/ LVCMOS logic.

The select and power-down inputs tolerate undershoot of -1V and overshoot of VCC + 1V. The MAX9176/ MAX9177 are available in 10-pin µMAX and 10-lead thin QFN packages, and operate from a single 3.3V supply over the -40°C to +85°C temperature range.

#### **Applications**

**Protection Switching** Loopback Clock Distribution

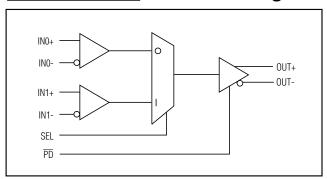

Functional Diagram appears at end of data sheet.

#### Features

- ♦ 1.0ps(RMS) Jitter (max) at 670MHz

- ♦ 68ps(P-P) Jitter at 800Mbps Data Rate

- ♦ 3.3V Supply

- **♦ LVDS Fail-Safe Inputs (MAX9176)**

- ♦ Anything Inputs (MAX9177) Accept CML/LVDS/LVPECL

- ♦ Select and Power-Down Inputs Tolerate -1.0V and Vcc + 1.0V

- ♦ Low-Power CMOS Design

- ♦ 10-Lead µMAX and QFN Packages

- ♦ -40°C to +85°C Operating Temperature Range

- ♦ Conform to ANSI TIA/EIA-644 LVDS Standard

- ♦ IEC61000-4-2 Level 4 ESD Rating

#### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE      |

|-------------|----------------|------------------|

| MAX9176EUB  | -40°C to +85°C | 10 μMAX          |

| MAX9176ETB* | -40°C to +85°C | 10 Thin QFN-EP** |

| MAX9177EUB  | -40°C to +85°C | 10 μMAX          |

| MAX9177ETB* | -40°C to +85°C | 10 Thin QFN-EP** |

<sup>\*</sup>Future product—contact factory for availability.

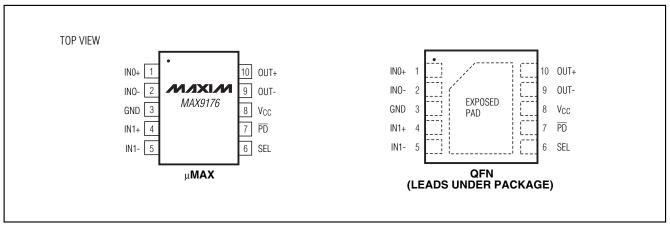

### **Pin Configurations**

MIXIM

Maxim Integrated Products 1

<sup>\*\*</sup>EP = Exposed paddle.

#### **ABSOLUTE MAXIMUM RATINGS**

| Vcc to GND                                            | 0.3V to +4.0V                    |

|-------------------------------------------------------|----------------------------------|

| IN_+, IN to GND                                       |                                  |

| OUT+, OUT- to GND                                     | 0.3V to +4.0V                    |

| PD, SEL to GND1.4                                     | $4V \text{ to } (V_{CC} + 1.4V)$ |

| Single-Ended and Differential Output                  |                                  |

| Short-Circuit Duration (OUT+, OUT-)                   | Continuous                       |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                                  |

| 10-Pin µMAX (derate 5.6mW/°C above +70°               | ,                                |

| 10-Lead Thin QFN (derate 24.4mW/°C above              | e +70°C)1951mW                   |

| Operating Temperature Range40°C to +85°C Maximum Junction Temperature+150°C Storage Temperature Range65°C to +150°C |

|---------------------------------------------------------------------------------------------------------------------|

| ESD Protection                                                                                                      |

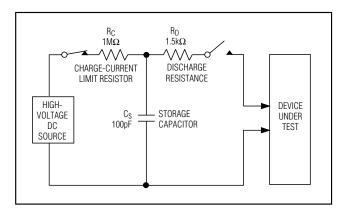

| Human Body Model (R <sub>D</sub> = 1.5k $\Omega$ , C <sub>S</sub> = 100pF)                                          |

| (IN_+, IN, OUT+, OUT-) <u>+</u> 16kV                                                                                |

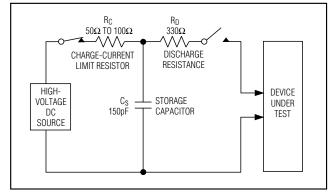

| IEC61000-4-2 Level 4 ( $R_D = 330\Omega$ , $C_S = 150pF$ )                                                          |

| Contact Discharge (IN_+, IN, OUT+, OUT-) <u>+</u> 8 kV                                                              |

| Air-Gap Discharge (IN_+, IN, OUT+, OUT-)                                                                            |

| Lead Temperature (soldering, 10s)+300°C                                                                             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = 3.0V \text{ to } 3.6V, R_L = 100\Omega, \overline{PD} = \text{high, SEL} = \text{high or low, differential input voltage } |V_{ID}| = 0.05V \text{ to } 1.2V, MAX9176 \text{ input common-mode voltage } V_{CM} = |V_{ID}/2| \text{ to } 2.4V - |V_{ID}/2|, MAX9177 \text{ input common-mode voltage } V_{CM} = |V_{ID}/2| \text{ to } V_{CC} - |V_{ID}/2|, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{CC} = 3.3V, |V_{ID}| = 0.2V, V_{CM} = 1.25V, T_A = +25^{\circ}\text{C}.) \text{ (Notes 1, 2, 3)}$

| PARAMETER                                                     | SYMBOL                              | CONDITIONS                                                                                  |                                                                                       | MIN   | TYP  | MAX      | UNITS |  |

|---------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------|------|----------|-------|--|

| DIFFERENTIAL INPUTS (IN_+, IN                                 | ·-)                                 |                                                                                             |                                                                                       |       |      |          |       |  |

| Differential Input High Threshold                             | V <sub>TH</sub>                     |                                                                                             |                                                                                       |       |      | +50      | mV    |  |

| Differential Input Low Threshold                              | V <sub>T</sub> L                    |                                                                                             |                                                                                       | -50   |      |          | mV    |  |

| Input Current                                                 | I <sub>IN+</sub> , I <sub>IN-</sub> | Figure 1                                                                                    |                                                                                       | -20   |      | +20      | μΑ    |  |

|                                                               |                                     | MAX9176                                                                                     | V <sub>CC</sub> = 0 or open,<br>Figure 1                                              |       |      |          |       |  |

| Power-Off Input Current                                       | IINO+,<br>IINO-                     | MAX9177                                                                                     | $V_{IN+} = 3.6V$ or 0,<br>$V_{IN-} = 3.6V$ or 0,<br>$V_{CC} = 0$ or open,<br>Figure 1 | -20   |      | +20      | μА    |  |

| Fail-Safe Input Resistors                                     | R <sub>IN1</sub>                    | V <sub>C</sub> C = 3.6V, 0 o                                                                | or open.                                                                              | 60    |      | 108      | 1     |  |

| (MAX9176)                                                     | R <sub>IN2</sub>                    | Figure 1                                                                                    |                                                                                       | 200   |      | 394      | kΩ    |  |

| Input Resistors<br>(MAX9177)                                  | R <sub>IN3</sub>                    | V <sub>CC</sub> = 3.6V, 0 or open,<br>Figure 1                                              |                                                                                       | 212   |      | 450      | kΩ    |  |

| Input Capacitance                                             | CIN                                 | IN_+ or IN to GND (Note 4)                                                                  |                                                                                       |       |      | 4.5      | рF    |  |

| LVTTL/LVCMOS INPUTS (SEL, F                                   | PD)                                 |                                                                                             |                                                                                       |       |      |          |       |  |

| Input High Voltage                                            | VIH                                 |                                                                                             |                                                                                       | 2.0   | V    | CC + 1.0 | V     |  |

| Input Low Voltage                                             | V <sub>IL</sub>                     |                                                                                             |                                                                                       | -1.0  |      | +0.8     | V     |  |

|                                                               |                                     | -1.0V ≤ SEL, PC                                                                             | Ō ≤ 0V                                                                                | -1.5  |      |          | mA    |  |

| Input Current                                                 | I <sub>IN</sub>                     | $0V \le SEL, \overline{PD} \le V_{CC}$<br>$V_{CC} \le SEL, \overline{PD} \le V_{CC} + 1.0V$ |                                                                                       | -20   |      | +20      | μΑ    |  |

|                                                               |                                     |                                                                                             |                                                                                       |       |      | +1.5     | mA    |  |

| LVDS OUTPUT (OUT+, OUT-)                                      |                                     |                                                                                             |                                                                                       |       |      |          |       |  |

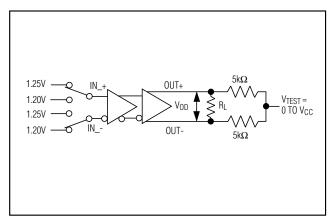

| Differential Output Voltage                                   | V <sub>OD</sub>                     | Figure 2                                                                                    |                                                                                       | 250   | 393  | 475      | mV    |  |

| Change in Differential Output<br>Voltage Between Logic States | ΔV <sub>OD</sub>                    | Figure 2                                                                                    |                                                                                       |       | 1.0  | 15       | mV    |  |

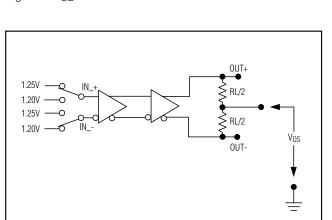

| Offset Voltage                                                | Vos                                 | Figure 3                                                                                    |                                                                                       | 1.125 | 1.25 | 1.375    | V     |  |

#### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC}=3.0V\ to\ 3.6V,\ R_L=100\Omega,\ \overline{PD}=high,\ SEL=high\ or\ low,\ differential\ input\ voltage\ |V_{ID}|=0.05V\ to\ 1.2V,\ MAX9176\ input\ common-mode\ voltage\ V_{CM}=|V_{ID}/2|\ to\ V_{CC}-|V_{ID}/2|,\ T_A=-40^{\circ}C\ to\ +85^{\circ}C,\ unless\ otherwise\ noted.$  Typical values are at  $V_{CC}=3.3V,\ |V_{ID}|=0.2V,\ V_{CM}=1.25V,\ T_A=+25^{\circ}C.)\ (Notes\ 1,\ 2,\ 3)$

| PARAMETER                                              | SYMBOL           | CON                                                                        | NDITIONS                                                     | MIN  | TYP   | MAX  | UNITS |

|--------------------------------------------------------|------------------|----------------------------------------------------------------------------|--------------------------------------------------------------|------|-------|------|-------|

| Change in Offset Voltage<br>Between Logic States       | ΔV <sub>OS</sub> | Figure 3                                                                   |                                                              |      | 4     | 15   | mV    |

| Fail-Safe Differential Output<br>Voltage (MAX9176)     | V <sub>OD</sub>  | Figure 2                                                                   |                                                              | 250  | 393   | 475  | mV    |

| Differential Output Resistance                         | RDIFF            | V <sub>CC</sub> = 3.6V or 0                                                |                                                              | 95   | 123   | 146  | Ω     |

| Power-Down Single-Ended<br>Output Current              |                  | <u> </u>                                                                   | V <sub>OUT+</sub> = open,<br>V <sub>OUT-</sub> = 3.6V or 0   | 1.0  | ±0.01 | +1.0 |       |

|                                                        | I <sub>PD</sub>  | PD = low                                                                   | V <sub>OUT-</sub> = open,<br>V <sub>OUT+</sub> = 3.6V or 0   | -1.0 |       |      | μΑ    |

| Power-Off Single-Ended Output                          | loff             | PD, SEL = low,<br>VCC = 0 or open                                          | V <sub>OUT+</sub> = open,<br>V <sub>OUT-</sub> = 3.6V or 0   | 4.0  | ±0.01 | +1.0 | μΑ    |

| Current                                                |                  |                                                                            | V <sub>OUT</sub> - = open,<br>V <sub>OUT</sub> + = 3.6V or 0 | -1.0 |       |      |       |

| Outrast Chart Circuit Coursest                         | 1                | V <sub>ID</sub> = +50mV or -50mV, V <sub>OUT+</sub> = 0 or V <sub>CC</sub> |                                                              | -15  |       | +15  | т Л   |

| Output Short-Circuit Current                           | IOS              | V <sub>ID</sub> = +50mV or -50mV, V <sub>OUT</sub> -= 0 or V <sub>CC</sub> |                                                              | -15  |       |      | mA    |

| Differential Output Short-Circuit<br>Current Magnitude | losp             | V <sub>ID</sub> = +50mV or -50mV, V <sub>OD</sub> = 0<br>(Note 4)          |                                                              |      |       | 15   | mA    |

| Supply Current                                         | Icc              | $R_L = 100\Omega$ , $\overline{PD} = V_{CC}$ , $SEL = V_{CC}$ or 0         |                                                              |      | 26    | 40   | mA    |

| Power-Down Supply Current                              | ICCPD            | $R_L = 100\Omega$ , $\overline{PD} = 0$ , other inputs open                |                                                              |      | 0.5   | 20   | μΑ    |

| Output Capacitance                                     | Co               | OUT+ or OUT- to G                                                          | ND (Note 4)                                                  |      |       | 5.2  | рF    |

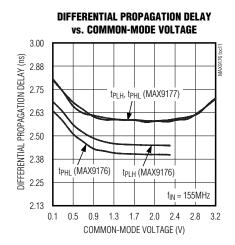

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 3.0V \text{ to } 3.6V, R_L = 100\Omega, C_L = 5pF, differential input voltage } |V_{ID}| = 0.15V \text{ to } 1.2V, MAX9176 input common-mode voltage } |V_{CM} = |V_{ID}/2| \text{ to } 2.4V - |V_{ID}/2|, MAX9177 input common-mode voltage } |V_{CM} = |V_{ID}/2| \text{ to } V_{CC} - |V_{ID}/2|, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, unless otherwise noted. Typical values are at } |V_{CC} = 3.3V, |V_{ID}| = 0.2V, V_{CM} = 1.25V, T_A = +25^{\circ}C.) \text{ (Notes 5, 6, 7)}$

| PARAMETER                      | SYMBOL            | CONDITIONS                                         |      | TYP  | MAX  | UNITS   |  |  |

|--------------------------------|-------------------|----------------------------------------------------|------|------|------|---------|--|--|

| DIFFERENTIAL INPUTS (IN_+, IN) |                   |                                                    |      |      |      |         |  |  |

| High-to-Low Propagation Delay  | tphl              | Figures 4, 5                                       | 1.33 | 2.46 | 3.23 | ns      |  |  |

| Low-to-High Propagation Delay  | tpLH              | Figures 4, 5                                       | 1.33 | 2.49 | 3.31 | ns      |  |  |

| Added Deterministic Jitter     | t <sub>DJ</sub>   | Figures 4, 5 (Notes 8, 12)                         |      | 68   | 80   | ps(P-P) |  |  |

| Added Random Jitter            | t <sub>RJ</sub>   | Figures 4, 5 (Note 12)                             |      | 0.7  | 1.0  | ps(RMS) |  |  |

| Pulse Skew   tpLH - tpHL       | tskp              | Figures 4, 5                                       |      | 27   | 142  | ps      |  |  |

| 5 5 6                          | tSKPP1            | Figures 4, 5 (Note 9)                              |      | 0.4  | 1.3  |         |  |  |

| Part-to-Part Skew              | tSKPP2            | Figures 4, 5 (Note 10)                             |      |      | 2.0  | ns      |  |  |

| Rise Time                      | t <sub>R</sub>    | Figures 4, 5                                       | 217  | 320  | 383  | ps      |  |  |

| Fall Time                      | tF                | Figures 4, 5                                       | 157  | 340  | 360  | ps      |  |  |

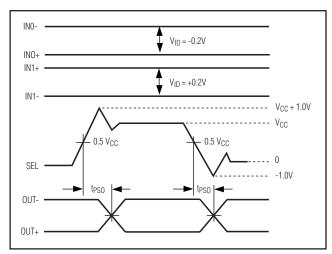

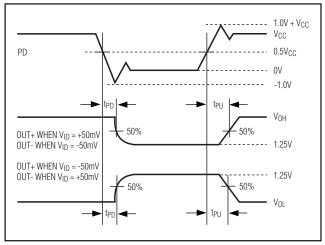

| Select to Out Delay            | tpso              | Figure 6                                           |      | 2.0  | 2.7  | ns      |  |  |

| Power-Down Time                | t <sub>PD</sub>   | Figures 7, 8                                       |      |      | 6.0  | ns      |  |  |

| Power-Up Time                  | tpu               | Figures 7, 8                                       |      |      | 35   | μs      |  |  |

| Maximum Data Rate              | DR <sub>MAX</sub> | Figures 4, 5,  V <sub>OD</sub>   ≥ 250mV (Note 11) | 800  |      |      | Mbps    |  |  |

| Maximum Switching Frequency    | f <sub>MAX</sub>  | Figures 4, 5,  V <sub>OD</sub>   ≥ 250mV (Note 11) | 670  |      |      | MHz     |  |  |

| Switching Supply Current       | lacou             | $f_{IN} = 670MHz$                                  |      | 38   | 58   | m ^     |  |  |

|                                | Iccsw             | $f_{IN} = 155MHz$                                  |      | 26   | 47   | mA      |  |  |

| PRBS Supply Current            | ICCPR             | DR = 800Mbps, 2 <sup>23</sup> - 1 PRBS input       |      | 27   | 49   | mA      |  |  |

- Note 1: Current into a pin is defined as positive. Current out of a pin is defined as negative. All voltages are referenced to ground except V<sub>TH</sub>, V<sub>TL</sub>, V<sub>ID</sub>, V<sub>OD</sub>, and ΔV<sub>OD</sub>.

- Note 2: Maximum and minimum limits over temperature are guaranteed by design and characterization. Devices are 100% tested at  $T_A = +25$ °C.

- Note 3: Tolerance on all external resistors (including figures) is  $\pm 1\%$ .

- Note 4: Guaranteed by design and characterization.

- Note 5: AC parameters are guaranteed by design and characterization and not production tested. Limits are set at ±6 sigma.

- **Note 6:** C<sub>L</sub> includes scope probe and test jig capacitance.

- Note 7: Pulse-generator output for differential inputs IN\_+, IN\_- (unless otherwise noted):  $f = 670 \underline{MHz}$ , 50% duty cycle,  $R_O = 50\Omega$ ,  $t_R = 500ps$ , and  $t_F = 500ps$  (0% to 100%). Pulse-generator output for single-ended inputs  $\overline{PD}$ , SEL:  $t_R = t_F = 1.5ns$  (0.2 $V_{CC}$  to 0.8 $V_{CC}$ ), 50% duty cycle,  $V_{OH} = V_{CC} + 1.0V$  settling to  $V_{CC}$ ,  $V_{OL} = -1.0V$  settling to zero.

- Note 8: Pulse-generator output for  $t_{DJ}$ :  $V_{OD} = 0.15V$ ,  $V_{OS} = 1.25V$ , bit rate = 800Mbps,  $2^{23}$  1 PRBS,  $R_{O} = 50\Omega$ ,  $t_{R} = 500$ ps, and  $t_{F} = 500$ ps (0% to 100%).

- **Note 9:** t<sub>SKPP1</sub> is the magnitude of the difference of any differential propagation delays between devices operating under identical conditions.

- Note 10: t<sub>SKPP2</sub> is the magnitude of the difference of any differential propagation delays between devices operating over rated conditions.

- Note 11: Meets all AC specifications.

- Note 12: Input jitter subtracted from output jitter.

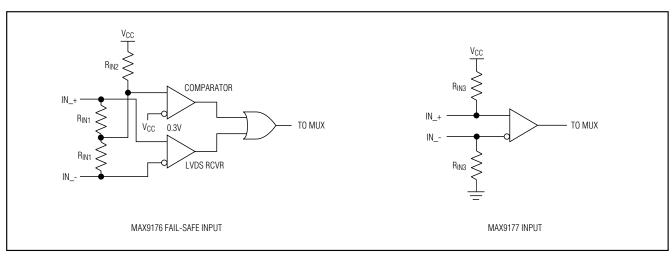

Figure 1. Input Structure

Figure 2. VoD Test Circuit

Figure 3. Vos Test Circuit

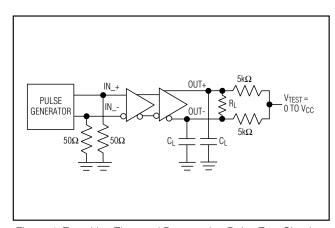

Figure 4. Transition Time and Propagation Delay Test Circuit

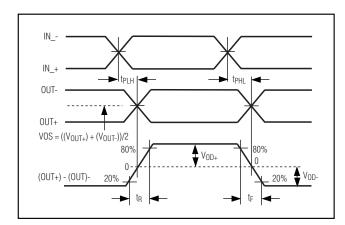

Figure 5. Transition Time and Propagation Delay Timing

Figure 6. Select-to-Out Delay Timing

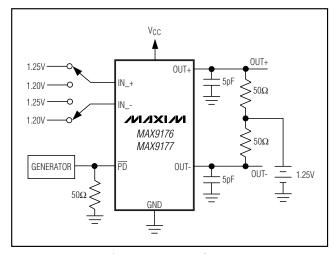

Figure 7. Power-Up/Down Delay Test Circuit

Figure 8. Power-Up/Down Delay Waveform

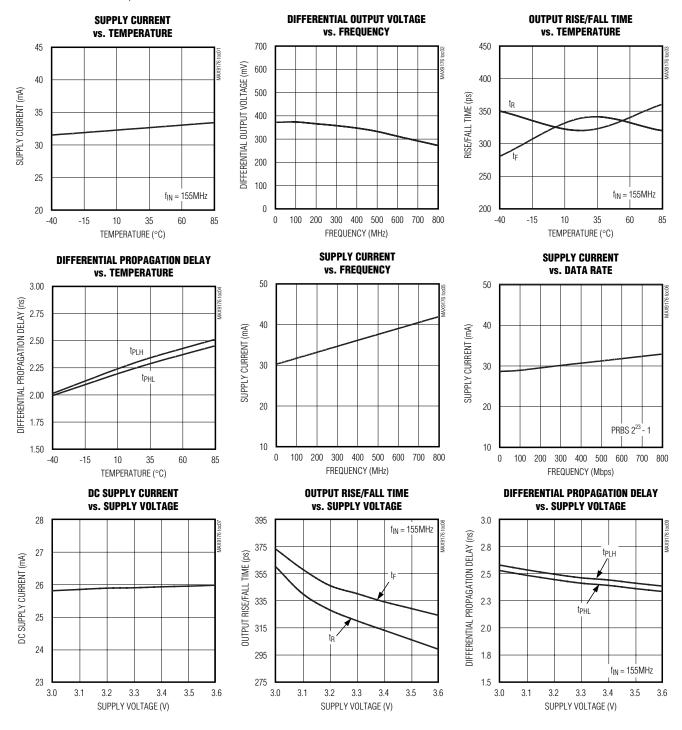

#### **Typical Operating Characteristics**

((MAX9176)  $V_{CC}$  = 3.3V,  $|V_{ID}|$  = 0.2V,  $V_{CM}$  = 1.25V,  $R_L$  = 100 $\Omega$ ,  $C_L$  = 5pf,  $\overline{PD}$  =  $V_{CC}$ , SEL = 0V, IN1+, IN1- = open,  $T_A$  = +25°C, unless otherwise noted.)

#### Typical Operating Characteristics (continued)

((MAX9176)  $V_{CC}=3.3V$ ,  $|V_{ID}|=0.2V$ ,  $V_{CM}=1.25V$ ,  $R_L=100\Omega$ ,  $C_L=5pf$ ,  $\overline{PD}=V_{CC}$ , SEL=0V, IN1+, IN1-=open,  $T_A=+25^{\circ}C$ , unless otherwise noted.)

### **Pin Description**

| Р    | PIN |             |                                                                                                                                                |  | FINATION |  |  |

|------|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|----------|--|--|

| μMAX | QFN | NAME        | FUNCTION                                                                                                                                       |  |          |  |  |

| 1    | 1   | INO+        | Noninverting Differential Input 0                                                                                                              |  |          |  |  |

| 2    | 2   | INO-        | Inverting Differential Input 0                                                                                                                 |  |          |  |  |

| 3    | 3   | GND         | Ground                                                                                                                                         |  |          |  |  |

| 4    | 4   | IN1+        | Noninverting Differential Input 1                                                                                                              |  |          |  |  |

| 5    | 5   | IN1-        | Inverting Differential Input 1                                                                                                                 |  |          |  |  |

| 6    | 6   | SEL         | LVTTL/LVCMOS Input Select. SEL = high selects differential input 1. SEL = low selects differential input 0. Internal pulldown resistor to GND. |  |          |  |  |

| 7    | 7   | PD          | LVTTL/LVCMOS Input. Device is powered down when $\overline{PD}$ is low. Internal pulldown resistor to GND.                                     |  |          |  |  |

| 8    | 8   | Vcc         | Power Supply                                                                                                                                   |  |          |  |  |

| 9    | 9   | OUT-        | Inverting Differential Output                                                                                                                  |  |          |  |  |

| 10   | 10  | OUT+        | Noninverting Differential Output                                                                                                               |  |          |  |  |

| _    | EP  | Exposed Pad | Exposed Pad. Solder to ground.                                                                                                                 |  |          |  |  |

8 \_\_\_\_\_\_ NIXI/N

**Table 1. Function Table**

|         | INPUTS                                                 | OUTPUT          |  |

|---------|--------------------------------------------------------|-----------------|--|

| (I)     | l_+) - (IN)                                            | (OUT+) - (OUT-) |  |

|         | ≥ +50mV                                                | Н               |  |

|         | ≤ -50mV                                                | L               |  |

| -50mV   | < V <sub>ID</sub> < +50mV                              | Indeterminate   |  |

| MAX9177 | Open                                                   |                 |  |

| MAX9176 | Open, undriven short, or undriven parallel termination | н               |  |

### Table 2. Input Select and Power-Down Function Table

| SEL       | PD        | OUT+, OUT-                                                                    |

|-----------|-----------|-------------------------------------------------------------------------------|

| Н         | Н         | IN1+, IN1-                                                                    |

| L or open | Н         | IN0+, IN0-                                                                    |

| X         | L or open | High impedance to ground and $123\Omega$ (typ) differential output resistance |

#### **Detailed Description**

The MAX9176/MAX9177 are 670MHz, low-jitter, low-skew 2:1 multiplexers ideal for protection switching, loopback, and clock distribution. The devices feature ultra-low 68ps(P-P) deterministic jitter that ensures reliable operation in high-speed links that are highly sensitive to timing error.

The MAX9176 has fail-safe LVDS inputs and an LVDS output. The MAX9177 has anything differential inputs (CML/LVDS/LVPECL) and an LVDS output. The output can be put into high impedance using the power-down input. The MAX9176 features fail-safe circuits that drive the output high when a selected input is open, undriven and shorted, or undriven and terminated. The MAX9177 has bias circuits that force the output high when a selected input is open. The mux select and power-down inputs are compatible with standard LVTTL/LVCMOS logic.

The select and power-down inputs tolerate undershoot of -1V and overshoot of V<sub>CC</sub> + 1V. The MAX9176/MAX9177 are available in 10-pin  $\mu$ MAX and 10-lead thin QFN packages, and operate from a single 3.3V supply over the -40°C to +85°C temperature range.

#### **Current-Mode LVDS Output**

The LVDS output uses a current-steering configuration. This approach results in less ground bounce and less output ringing, enhancing noise margin and system speed performance.

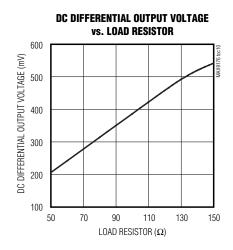

A differential output voltage is produced by steering current through the parallel combination of the integrated differential output resistor and transmission line impedance/termination resistor. When driving a  $100\Omega$  load, a differential voltage of 250mV to 475mV is produced. For loads greater than  $100\Omega,$  the output voltage is larger, and for loads less than  $100\Omega,$  the output volt-

age is smaller. See the Differential Output Voltage vs. Load Resistance curve in *Typical Operating Characteristics* for more information. The output is short-circuit current limited for single-ended and differential shorts.

#### MAX9176 Input Fail-Safe

The fail-safe feature of the MAX9176 sets the output high when the differential input is:

- Open

- Undriven and shorted

- Undriven and terminated

Without a fail-safe circuit, when the selected input is undriven, noise at the input may switch the output and it may appear to the system that data is being sent. Open or undriven terminated input conditions can occur when a cable is disconnected or cut, or when the driver output is in high impedance. A shorted input can occur because of a cable failure.

When the selected input is driven with a differential signal of  $|V_{ID}| = 50$ mV to 1.2V within a voltage range of 0 to 2.4V, the fail-safe circuit is not activated. If the selected input is open, undriven and shorted, or undriven and terminated, an internal resistor in the fail-safe circuit pulls both inputs above  $V_{CC}$  - 0.3V, activating the fail-safe circuit and forcing the output high (Figure 1).

#### Overshoot and Undershoot Voltage Protection

The MAX9176/MAX9177 are designed to protect the select and power-down inputs (SEL and  $\overline{PD}$ ) against latchup due to transient overshoot and undershoot voltage. If the input voltage goes above VCC or below GND by up to 1V, an internal circuit limits input current to 1.5mA.

#### **Applications Information**

#### **Power-Supply Bypassing**

Bypass the  $V_{CC}$  pin with high-frequency surface-mount ceramic 0.1 $\mu$ F and 0.001 $\mu$ F capacitors in parallel as close to the device as possible, with the smaller valued capacitor closest to  $V_{CC}$ .

#### **Differential Traces**

Input and output trace characteristics affect the performance of the MAX9176/MAX9177. Use controlled-impedance differential traces ( $100\Omega$  typical). To reduce radiated noise and ensure that noise couples as common mode, route the differential input and output signals within a pair close together. Reduce skew by matching the electrical length of the two signal paths that make up the differential pair. Excessive skew can result in a degradation of magnetic field cancellation. Maintain a constant distance between the differential traces to avoid discontinuities in differential impedance. Minimize the number of vias to further prevent impedance discontinuities.

#### **Cables and Connectors**

Interconnect for LVDS typically has a controlled differential impedance of  $100\Omega$ . Use cables and connectors that have matched differential impedance to minimize impedance discontinuities.

Avoid the use of unbalanced cables such as ribbon or simple coaxial cable. Balanced cables such as twisted pair offer superior signal quality and tend to generate less EMI due to magnetic field canceling effects. Balanced cables pick up noise as common mode, which is rejected by the LVDS receiver.

#### **Termination**

The MAX9176/MAX9177 require external input and output termination resistors. For LVDS, connect an input termination resistor across each differential input and at the far end of the interconnect driven by the LVDS output. Place the input termination resistor as close to the receiver input as possible. Termination resistors should match the differential impedance of the transmission line. Use 1% surface-mount resistors.

The MAX9176/MAX9177 feature an integrated differential output resistor. This resistor reduces jitter by damping reflections produced by any mismatch between the transmission line and termination resistor at the far end of the interconnect.

#### **Board Layout**

Separate the differential and single-ended signals to reduce crosstalk. A four-layer printed circuit board with separate layers for power, ground, differential signals,

and single-ended logic signals is recommended. Separate the differential signals from the logic signals with power and ground planes for best results.

#### IEC 61000-4-2 Level 4 ESD Protection

The IEC 61000-4-2 standard (Figure 10) specifies ESD tolerance for electronic systems. The IEC61000-4-2 model specifies a 150pF capacitor that is discharged into the device through a 330 $\Omega$  resistor. The MAX9176/MAX9177 differential inputs and outputs are rated for IEC61000-4-2 level 4 (±8kV Contact Discharge and ±15kV Air-Gap Discharge). The Human Body Model (HBM, Figure 9) specifies a 100pF capacitor that is discharged into the device through a 1.5k $\Omega$  resistor.

IEC 61000-4-2 level 4 discharges higher peak current and more energy than the HBM due to the lower series resistance and larger capacitor.

Figure 9. Human Body Test Model

Figure 10. IEC 61000\_4-2 Contact Discharge Test Model

### Functional Diagram

**Chip Information**

TRANSISTOR COUNT: 744

PROCESS: CMOS

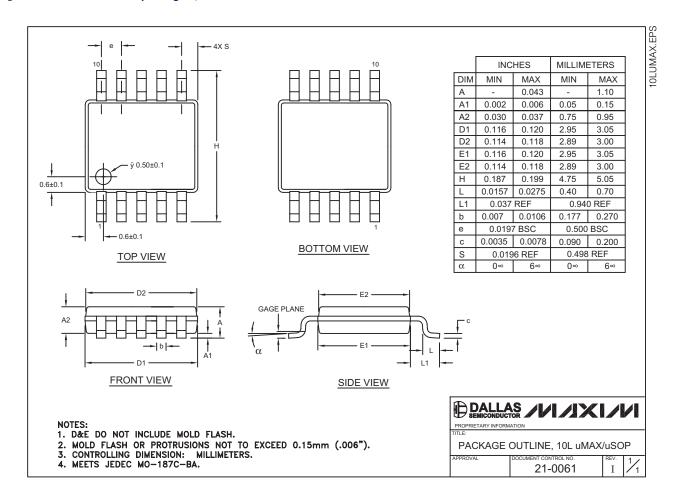

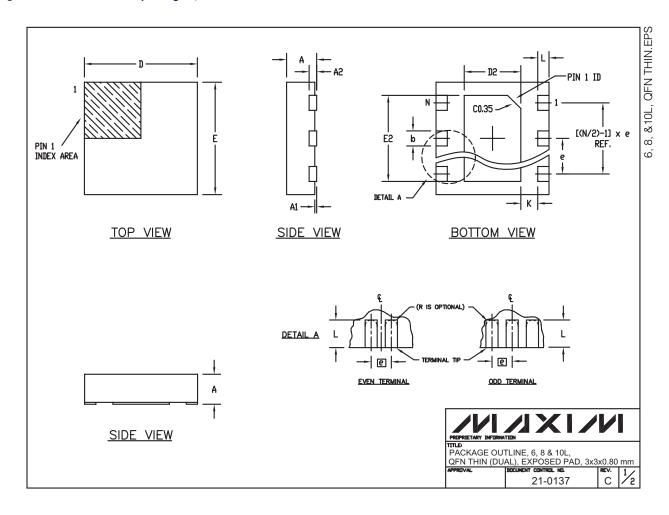

#### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

#### **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

#### **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

| COMMON DIMENSIONS |           |      |  |  |  |

|-------------------|-----------|------|--|--|--|

| SYMBOL            | MIN.      | MAX. |  |  |  |

| Α                 | 0.70      | 0.80 |  |  |  |

| D                 | 2.90      | 3.10 |  |  |  |

| E                 | 2.90      | 3.10 |  |  |  |

| A1                | 0.00      | 0.05 |  |  |  |

| L                 | 0.20      | 0.40 |  |  |  |

| k                 | 0.25 MIN  |      |  |  |  |

| A2                | 0.20 REF. |      |  |  |  |

| PACKAGE VARIATIONS |    |           |           |          |                |           |               |

|--------------------|----|-----------|-----------|----------|----------------|-----------|---------------|

| PKG. CODE          | N  | D2        | E2        | е        | JEDEC SPEC     | b         | [(N/2)-1] x e |

| T633-1             | 6  | 1.50±0.10 | 2.30±0.10 | 0.95 BSC | MO229 / WEEA   | 0.40±0.05 | 1.90 REF      |

| T833-1             | 8  | 1.50±0.10 | 2.30±0.10 | 0.65 BSC | MO229 / WEEC   | 0.30±0.05 | 1.95 REF      |

| T1033-1            | 10 | 1.50±0.10 | 2.30±0.10 | 0.50 BSC | MO229 / WEED-3 | 0.25±0.05 | 2.00 REF      |

- 1. ALL DIMENSIONS ARE IN mm. ANGLES IN DEGREES.

2. COPLANARITY SHALL NOT EXCEED 0.08 mm.

3. WARPAGE SHALL NOT EXCEED 0.10 mm.

- 4. PACKAGE LENGTH/PACKAGE WIDTH ARE CONSIDERED AS

- SPECIAL CHARACTERISTIC(S).

5. DRAWING CONFORMS TO JEDEC MO220.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.